Overview

A Digital Down Converter performs channel access functions in digital receivers. It is used for extracting a channel (frequency band) of interest in a wideband signal. Abaco Systems' wideband DDC core employs a quad DDC architecture to achieve ultra high performances. The core accepts up to 16-bit complex data and can process 1GSPS continuously. With a fully programmable architecture at all stages of the processing, this core combines flexibility and speed and can be used in combination with our dual-channel 1GSPS ADC module.

Input stage

Four 16-bit complex samples can be loaded to the core in parallel at a rate of 250MHz, thus providing an input bandwidth of 1GSPS. The input gain, implemented using multipliers, is user programmable.

NCO

The Numerically Controlled Oscillator architecture comprises four sets of sine and cosine directly applied to the mixers.

Mixer stage

The core implements four mixers in parallel in order to keep up with the input rate. FIR filters, with user-programmable filter coefficients, process the data after the mixer stage. The output of the filters can be decimated by a factor in the range 4 to 256.

Output stage

The output data format is user programmable and ranges from 16 to 32 bits. Customized DDC cores are available upon request.

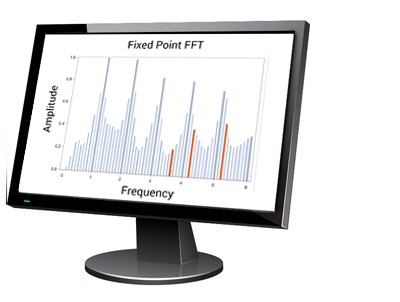

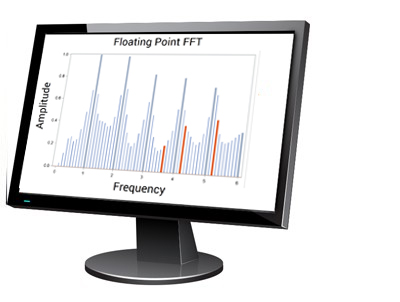

StellarIP is available for this product. A simple way to design FPGA firmware with automated code and bitstream generation. A fully functional VHDL test bench and Matlab functions are delivered along the wideband DDC core for simulation purposes and specific performance characterization.

Downloads

White Papers

Solutions Briefs

Request A Quote

Wideband Digital Down Converter

Contact An Expert

Looking for help with Wideband Digital Down Converter

Get Support

Looking for help with Wideband Digital Down Converter